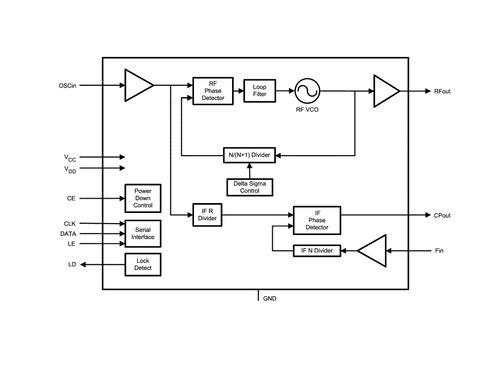

LMX2502是一款高性能、集成压控振荡器(VCO)的锁相环(PLL)频率合成器,专为无线通信、测试测量和射频系统设计。本技术手册将详细介绍其系统集成的关键技术和设计考量。

1. 概述与特性

LMX2502的核心优势在于其高度集成性。它将低噪声PLL内核、高性能集成VCO、精密电荷泵以及可编程分频器集成于单一芯片。其频率覆盖范围广泛(具体取决于型号版本),支持小数N分频和整数N分频模式,具有卓越的相位噪声性能和快速锁定时间。该器件通常通过串行外设接口(SPI)进行编程与控制。

2. 关键系统集成模块

a. 参考时钟输入:需要一个洁净、低抖动的参考时钟源。建议使用晶体振荡器或高质量的TCXO。参考时钟通过内部R分频器进行处理,其稳定性和相位噪声直接影响整个环路的性能。

b. 集成VCO与环路滤波器:LMX2502集成了VCO,简化了外部电路设计。外部环路滤波器的设计至关重要,它决定了锁相环的动态特性,如锁定速度、相位噪声和杂散抑制。必须根据所需的带宽、相位裕度和抑制需求,精心计算滤波器元件的值(电阻、电容)。

c. 射频输出:合成后的射频信号从芯片输出。为确保信号完整性,输出路径的PCB布局应遵循微波设计原则,使用受控阻抗微带线,并尽量减少不连续性。输出端可能需要额外的缓冲放大器或衰减器以满足系统电平要求。

d. 电源管理:LMX2502对电源噪声敏感。必须提供高度稳定、低噪声的供电。推荐采用多级滤波方案:使用铁氧体磁珠或小值电感与去耦电容(如10μF、0.1μF、10pF组合)构成π型滤波器,分别对模拟和数字电源引脚进行去耦。电源平面应保持完整,避免高频噪声串扰。

e. SPI控制接口:与微控制器(MCU)或FPGA的连接需确保信号完整性。在长走线或噪声环境中,建议串联小电阻以阻尼振铃,并考虑在靠近芯片的SCLK、SDI、LE引脚对地添加小电容以滤除高频噪声。

- PCB布局与电磁兼容性(EMC)设计

- 接地策略:采用坚固的接地平面,为所有接地引脚提供低阻抗回路。将模拟地(AVDD相关)和数字地(DVDD、SPI相关)在芯片下方单点连接,以防止数字噪声污染敏感的模拟电路。

- 元件放置:去耦电容应尽可能靠近对应的电源引脚。环路滤波器元件应紧靠相关引脚(如CPout)放置,避免引入寄生电感和串扰。

- 屏蔽与隔离:在要求苛刻的应用中,可考虑使用屏蔽罩将PLL区域与其他高频或数字电路隔离,以进一步降低干扰。

4. 软件配置与校准流程

系统上电后,需通过SPI接口配置一系列寄存器,包括设置参考分频比、N分频比(整数/小数)、电荷泵电流、VCO子带选择等。对于集成VCO,通常需要执行校准例程(如自动VCO频带选择),以确保在目标频率下工作在最优增益和相位噪声点。软件应按照数据手册中的序列进行初始化。

5. 系统验证与故障排查

集成后,需验证关键性能指标:

- 相位噪声与近端杂散。

- 锁定时间(频率切换速度)。

- 输出功率和频谱纯度。

常见问题包括相位噪声恶化、杂散过高或无法锁定,通常可追溯至参考时钟质量差、环路滤波器设计不当、电源噪声或PCB布局缺陷。

结论:成功集成LMX2502频率合成器系统,依赖于对器件特性的深入理解、精心的外围电路(尤其是环路滤波器和电源)设计、严谨的PCB布局以及正确的软件初始化。遵循本指南中的设计原则,将有助于实现稳定、高性能的射频频率合成解决方案。