声纳技术作为水下探测、通信与导航的核心手段,其小型化、低功耗与高性能集成是当前研究的热点。现场可编程门阵列(FPGA)以其并行处理能力强、可重构性高以及功耗相对可控等优势,成为实现小型声纳片上系统(SoC)集成的理想平台。本文将深入探讨基于FPGA的小型声纳片上系统集成的关键技术、系统架构设计以及未来发展趋势。

一、FPGA在小型声纳系统集成中的核心优势

与传统的基于通用处理器(如DSP、GPU)或全定制ASIC的方案相比,FPGA在小型声纳系统中展现出独特价值:

- 高度并行处理能力:声纳信号处理,尤其是波束形成、脉冲压缩、滤波等算法,天然适合并行计算。FPGA的硬件并行性可以极大加速这些计算密集型任务,满足实时性要求。

- 灵活的可重构性:声纳系统可能需要根据不同的工作模式(如主动探测、被动监听、通信)切换信号处理链。FPGA允许在系统层面进行动态重构,无需更改硬件即可实现功能切换与算法升级。

- 集成与功耗平衡:现代FPGA内部集成了高性能硬核(如ARM处理器)、高速收发器、模数转换接口等,能够将数字信号处理、控制逻辑、接口通信等模块高度集成于单一芯片,有效减小系统体积与功耗,这对于小型化平台(如自主水下航行器AUV、便携设备)至关重要。

- 确定性低延迟:FPGA的硬件逻辑执行具有确定性和极低的延迟,对于声纳系统,尤其是主动声纳的发射/接收同步、快速目标跟踪等关键时序控制极为有利。

二、基于FPGA的小型声纳片上系统架构设计

一个典型的集成化小型声纳SoC在FPGA上的实现,通常采用软硬件协同设计的思路,其核心架构可分为以下几个层次:

- 硬件平台层:

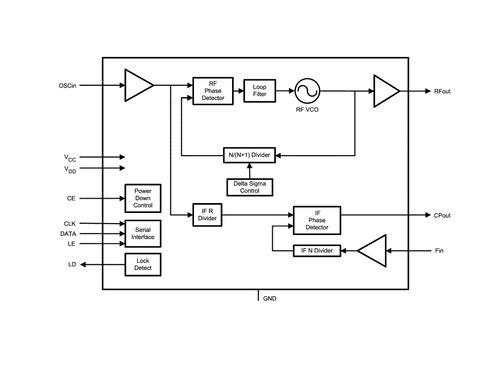

- 核心FPGA芯片:选择具有足够逻辑资源、DSP单元、内存带宽和I/O接口的器件。

- 外围电路:包括前置放大器、抗混叠滤波器、高速高精度ADC/DAC(或利用FPGA集成的高速串行接口连接外部转换器)、电源管理、时钟网络等。

- 片上系统架构层(关键集成部分):

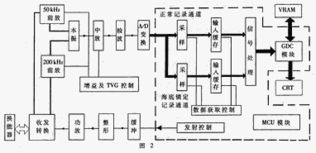

- 数据采集与接口模块:负责控制ADC采集多路换能器信号,并通过高速接口(如JESD204B)将数据流送入FPGA处理核心。

- 高速数字信号处理流水线:这是系统的核心,通常在FPGA逻辑资源中实现。包括:

- 数字下变频与滤波

- 波束形成器(时域或频域):利用FPGA的并行性实现多通道实时波束形成。

- 脉冲压缩(匹配滤波)

- 动态范围压缩、门限检测等。

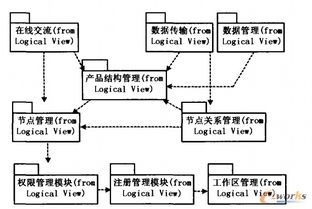

- 处理器系统:利用FPGA内部的硬核或软核处理器(如ARM Cortex-A/M系列,或RISC-V软核)运行上层应用、系统控制、数据融合、网络通信(如以太网)及用户界面等任务。

- 片上互连与存储器:通过AXI等片上总线协议,高效连接处理器系统与硬件加速引擎(DSP流水线)、外部DDR内存控制器以及各类外设IP核,实现数据的高吞吐量传输与共享。

- 发射信号生成模块:根据声纳波形要求,生成高精度的发射信号,通过DAC驱动功率放大器。

- 软件/固件层:

- 运行在处理器上的嵌入式操作系统(如Linux RT)及驱动。

- 信号处理算法的硬件描述语言(如VHDL/Verilog)实现。

- 高层次综合(HLS)工具可能用于将部分C/C++算法自动转换为硬件逻辑,提高开发效率。

三、系统集成中的关键挑战与应对策略

- 算法硬件化实现:将复杂的声纳信号处理算法高效映射到FPGA硬件逻辑中,需要深入的算法优化(如定点化、流水线设计、资源复用)和硬件设计技巧。

- 系统同步与时序:多通道数据采集、处理与发射的严格同步是声纳性能的保证。需精心设计时钟树、触发机制和时序约束。

- 功耗与散热管理:小型化系统对功耗敏感。需采用时钟门控、动态电压频率调节、选择低功耗器件型号以及优化算法硬件实现来降低功耗。

- 开发复杂度:集成处理器、硬件加速器、多种接口的SoC设计复杂度高。利用成熟的IP核、参考设计以及SoC开发工具链(如Xilinx Vitis或Intel Quartus)可以显著降低开发门槛。

四、未来展望

随着FPGA技术的不断发展,未来小型声纳片上系统集成将呈现以下趋势:

- 更高程度的异构集成:FPGA将集成更多专用AI加速引擎(如用于神经网络目标识别的NPU),实现“信号处理+智能识别”的一体化片上系统。

- 3D堆叠与先进封装:通过芯片堆叠技术,将FPGA、高带宽内存(HBM)、模拟前端等异构芯片集成于同一封装,实现极致的性能、功耗与体积平衡。

- 软硬件协同设计自动化:更高层次的工具将使算法工程师更直接地将模型部署到FPGA硬件,进一步缩短开发周期。

- 标准化与模块化:形成基于FPGA的声纳处理IP核库和标准接口,促进不同功能模块的快速集成与系统复用。

结论

利用FPGA实现小型声纳的片上系统集成,是满足现代水下探测设备对高性能、低功耗、小体积及高灵活性需求的战略性技术路径。通过精心的软硬件协同架构设计,能够将数据采集、实时信号处理、智能决策与控制高度集成于单一芯片平台,极大地推动了声纳设备的微型化与智能化进程。尽管面临设计复杂性与功耗管理等挑战,但随着FPGA生态与设计工具的成熟,基于FPGA的集成化声纳SoC必将成为未来水下技术领域的重要基石。